AMD ซุ่มพัฒนา EPYC Venice ชิปตัวแรง 2nm 256 คอร์ เจอตัวจริงปลายปีนี้

AMD กำลังจะสรา้งความสั่นสะเทือนให้วงการเซิร์ฟเวอร์และดาต้าเซ็นเตอร์อีกครั้ง ด้วยการเปิดเผยข้อมูลของซีพียูตัวใหม่ล่าสุด นั่นคือ EPYC “Venice” ที่พัฒนาบนสถาปัตยกรรม Zen 6 ในงาน Advancing AI 2025 ที่ผ่านมา โดยถือเป็นก้าวกระโดดครั้งใหญ่ของ AMD ในการเตรียมรับมือกับยุคของปัญญาประดิษฐ์ (AI) และการประมวลผลระดับสูง (HPC – High Performance Computing)

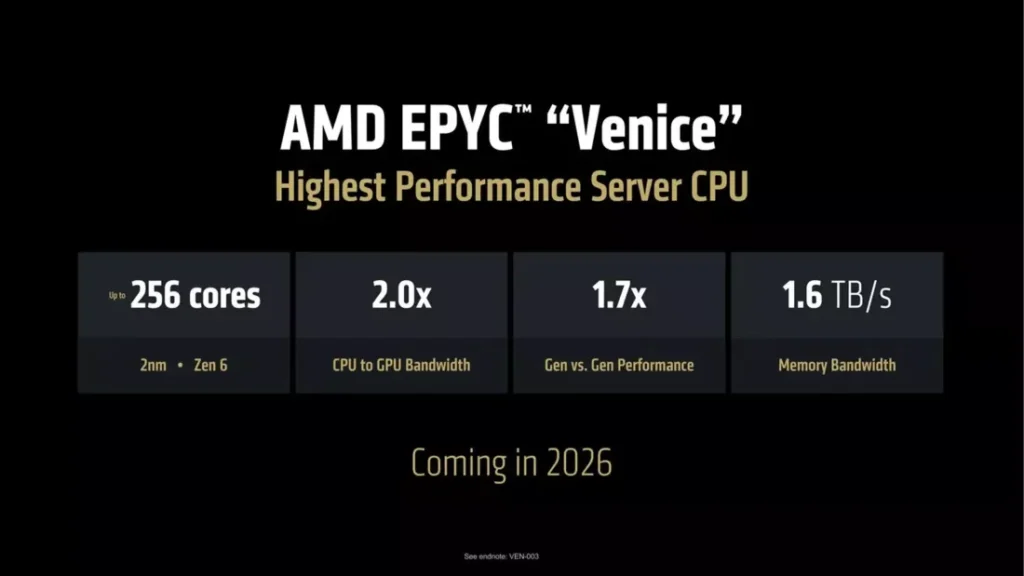

Venice เป็นซีพียูเซิร์ฟเวอร์ในตระกูล EPYC รุ่นที่ 6 ซึ่งใช้สถาปัตยกรรม Zen 6 และ Zen 6c โดยใช้เทคโนโลยีการผลิตระดับ 2 นาโนเมตรจาก TSMC และมีจำนวนคอร์มากถึง 256 คอร์— นับเป็นชิปเซิร์ฟเวอร์รุ่นแรกของโลกที่ใช้เทคโนโลยีขั้นสูงระดับนี้

ชิป EPYC Venice จาก AMD ถือเป็นก้าวกระโดดด้านประสิทธิภาพ ด้วยการรองรับสูงสุด 256 คอร์สถาปัตยกรรม Zen 6 เพิ่มขึ้นถึง 33% จากรุ่นก่อนหน้าอย่าง EPYC Turin ที่รองรับได้สูงสุด 192 คอร์ นอกจากนี้ AMD ระบุว่า Venice จะให้ ประสิทธิภาพโดยรวมเพิ่มขึ้นถึง 70% เมื่อเทียบกับ Turin ซึ่งมาจากจำนวนคอร์ที่เพิ่มขึ้นเท่านั้น แต่ยังรวมถึงการปรับปรุงด้านประสิทธิภาพต่อคอร์ และการออกแบบสถาปัตยกรรมภายในใหม่ทั้งหมด

ไม่ว่าจะเป็น เทคโนโลยีการผลิตระดับ 2 นาโนเมตรของ TSMC ซึ่งช่วยให้ AMD สามารถใส่ทรานซิสเตอร์ได้มากขึ้นในพื้นที่เท่าเดิม ส่งผลให้ได้ทั้งประสิทธิภาพที่สูงขึ้น และการใช้พลังงานที่มีประสิทธิภาพยิ่งกว่าเดิม

แบนด์วิดท์ของหน่วยความจำต่อซ็อกเก็ตที่เพิ่มขึ้นกว่าเท่าตัว จาก 614 GB/s ในรุ่นปัจจุบัน เป็นสูงสุดถึง 1.6 TB/s มาจากการรองรับ DDR5 สูงสุด 16 แชนเนล พร้อมรองรับเทคโนโลยีหน่วยความจำขั้นสูงอย่าง MR-DIMM และ MCR-DIMM การเพิ่มประสิทธิภาพนี้มีความสำคัญอย่างมาก โดยเฉพาะในการประมวลผลเวิร์กโหลดขนาดใหญ่ เช่น AI และการวิเคราะห์ข้อมูล ที่ต้องป้อนข้อมูลเข้าคอร์ประสิทธิภาพสูงอย่างต่อเนื่องและรวดเร็ว

นอกจากนี้ AMD ยังออกแบบ Venice เพื่อตอบโจทย์ความต้องการด้านการเชื่อมต่อระหว่าง CPU และ GPU ที่รวดเร็วยิ่งขึ้น โดยเพิ่มแบนด์วิดท์การสื่อสารระหว่าง CPU-GPU ขึ้นเป็น 2 เท่า ซึ่งคาดว่าจะเป็นผลจากการรองรับ PCI Express 6.0 ที่มีเลนสูงสุดถึง 128 PCIe lanes ทำให้สามารถรับส่งข้อมูลได้สูงสุดถึง 128 GB/s ต่อทิศทาง (ไม่รวม overhead จาก encoding) ซึ่งเป็นหัวใจสำคัญของการฝึกและประมวลผลโมเดล AI ที่ต้องอาศัยการรับส่งข้อมูลระหว่างโปรเซสเซอร์และตัวเร่งความเร็วอย่างมหาศาล

AMD เตรียมเปิดตัว Venice ใน 2 รุ่นหลัก ได้แก่: รุ่นมาตรฐาน Zen 6 มีคอร์สูงสุด 96 คอร์ และรุ่น High Density Zen 6c มีคอร์สูงสุด 256 คอร์ 512 เธรด

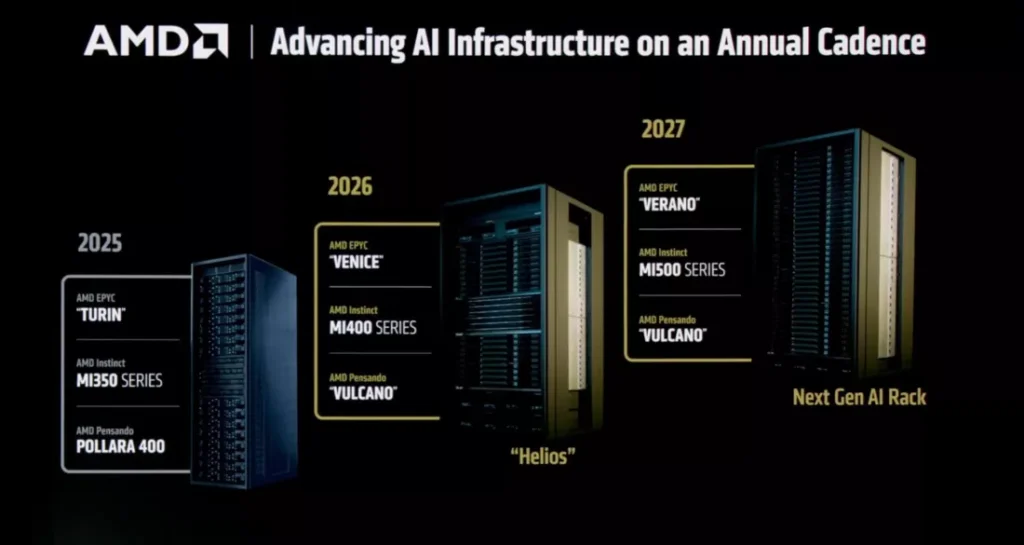

จากข้อมูลล่าสุด AMD คาดว่าจะเริ่มผลิต Venice ในปลายปี 2025 และจะพร้อมวางจำหน่ายในตลาดดาต้าเซ็นเตอร์ในช่วง ครึ่งหลังของปี 2026 (H2 2026) โดย Venice จะมาเป็นผู้นำในสายการผลิตชิป EPYC รุ่นที่ 6 ก่อนที่รุ่นย่อยอื่นๆ จะตามมาในลำดับถัดไป

ในระยะยาว Venice จะกลายเป็นหัวใจของสถาปัตยกรรมระดับแร็คแบบใหม่ที่ชื่อว่า Helios ซึ่ง AMD วางแผนจะรวมซีพียู Venice เข้ากับ GPU ตระกูลใหม่ Instinct MI400 และระบบเครือข่ายความเร็วสูง เพื่อสร้างแพลตฟอร์มแบบรวมศูนย์ที่ออกแบบมาสำหรับงาน AI โดยเฉพาะ ทั้งในแง่ประสิทธิภาพการฝึกโมเดล การประมวลผล และปริมาณข้อมูลหน่วยความจำขนาดใหญ่ที่จะรองรับเวิร์กโหลดระดับยุคถัดไปได้อย่างเต็มที่